Hi. I'm Shivangi Gambhir.

I am currently residing in New Delhi.

I completed my high school from Kalpa Co-Educational School,Hyderabad and finished my secondary school from FIITJEE,Hyderabad.

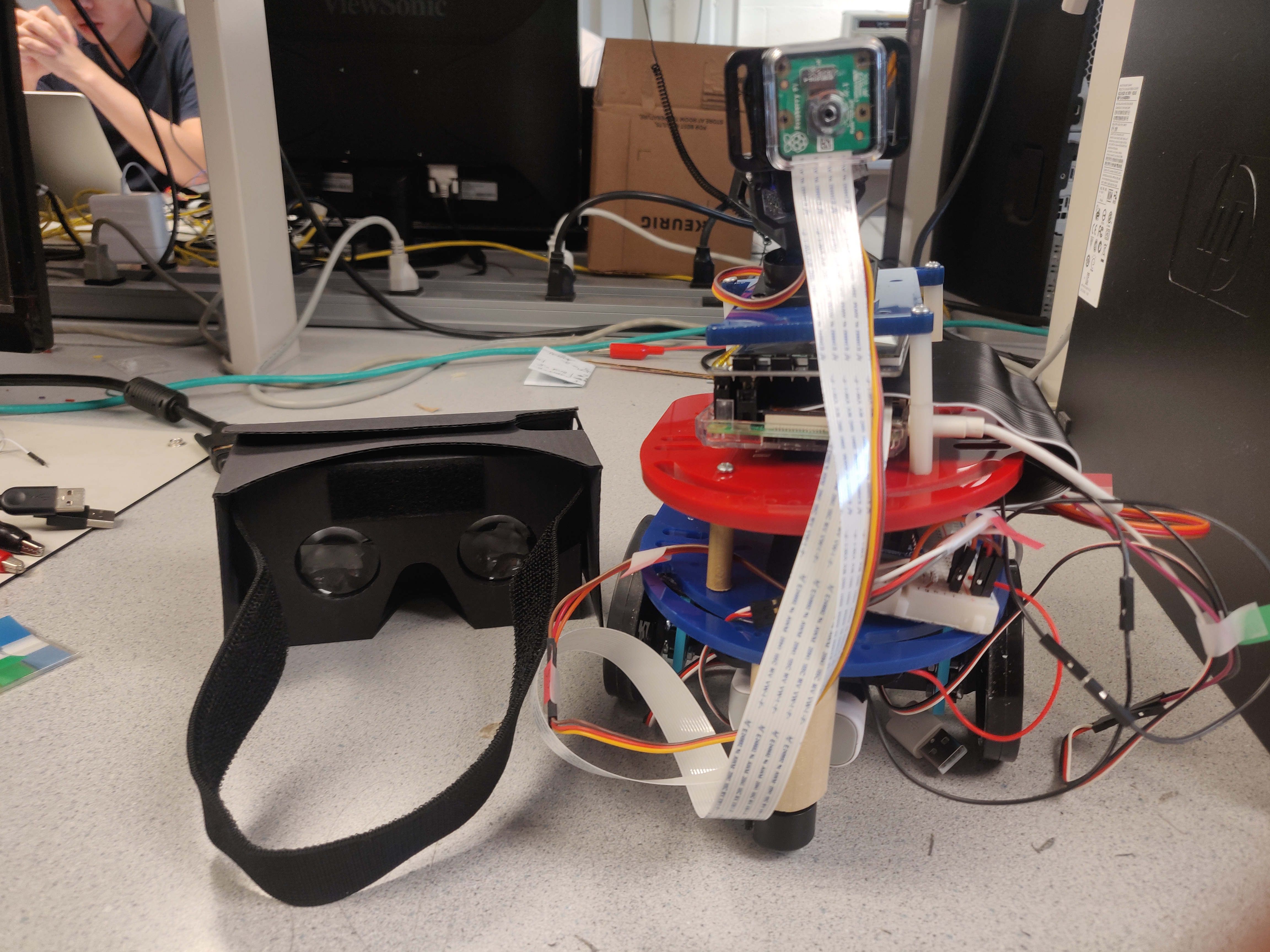

I completed my undergraduate studies in the Electronics and Communication Engineering department from Manipal Institute of Technology,Manipal.

I am currently a Masters/Graduate student at Cornell University specializing in the Electrical and Computer Engineering

Discipline. My inquisitiveness and immense passion in Computer Architecture and Chip Designing has led me to

actively work and contribute on related projects. With two years work experience in Qualcomm and

the skills I'll be honing at Cornell, I look forward to explore/work in the world of chips & processors.